序号 | 类型 | 描述 |

1 | 2D SiP | 在同一个封装基板上将芯片一个挨一个的排列以二维的模式封装在一个封装体内 |

2 | 2.5D SiP | 在一个封装中采用物理的方法将两个或多个芯片堆叠整合起来进行封装。/ y9 ^7 G$ d2 L! y; ]1 W( k |

3 | 3D SiP | 在2D封装的基础上,把多个裸芯、封装芯片、多芯片甚至圆片进行叠层互联,构成立体封装,这种结构也称作叠层型3D封装。9 d8 _' ?" o5 } c |

序号 | 应用领域 | 详细描述 |

1 | 汽车电子 | 汽车电子里的SiP应用以发动机控制单元(ECU)举例,ECU由微处理器(CPU)、存储器(ROM、RAM)、输入/输出接口(I/O)、模数转换器(A/D)以及整形、驱动等大规模集成电路组成。各类型的芯片之间工艺不同,目前较多采用SiP的方式将芯片整合在一起成为完整的控制系统. o, c- h5 [+ T. D* N |

2 | 医疗电子 | 该领域的典型应用为可植入式电子医疗器件,比如胶囊式内窥镜。内窥镜由光学镜头、图像处理芯片、射频信号发射器、天线、电池等组成。 |

3 | GUP | SiP在计算机领域的应用主要来自于将处理器和存储器集成在一起。4 H v S- R4 _) r' `& | |

4 | 消费类电子 | 包括了ISP(图像处理芯片)、蓝牙芯片等。8 I) t$ N: a% B$ L9 D- I( h |

5 | 蓝牙系统 | 一般由无线部分、链路控制部分、链路管理支持部分和主终端接口组成,SiP技术可以使蓝牙做得越来越小迎合了市场的需求,从而大力推动了蓝牙技术的应用。 |

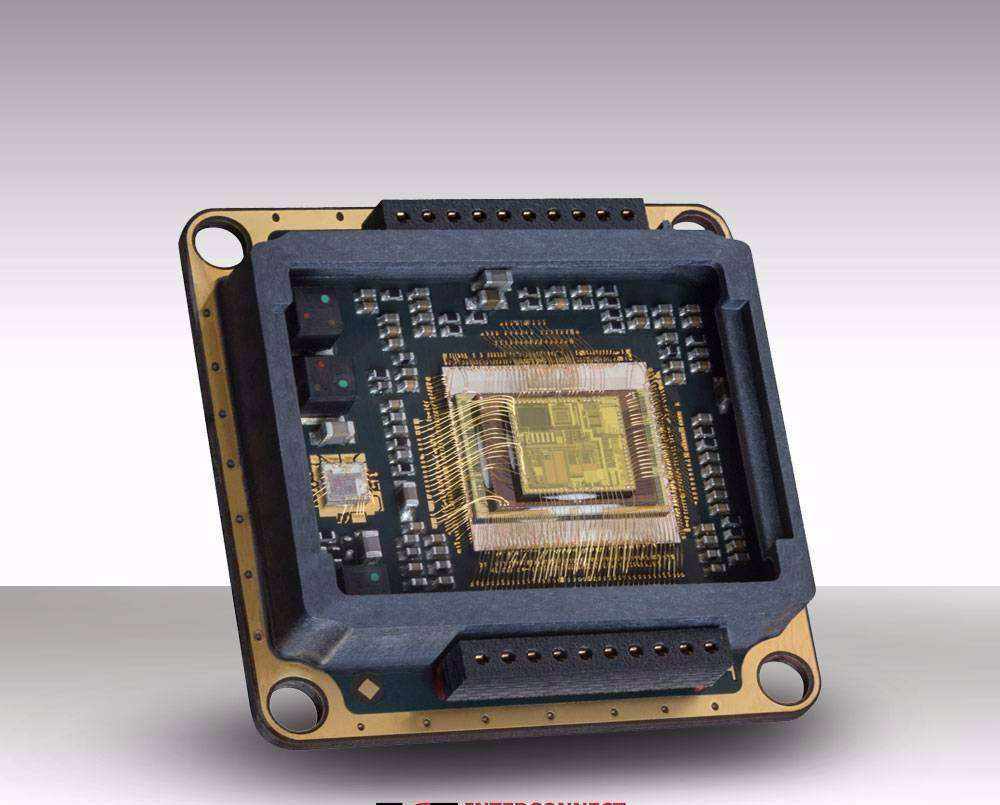

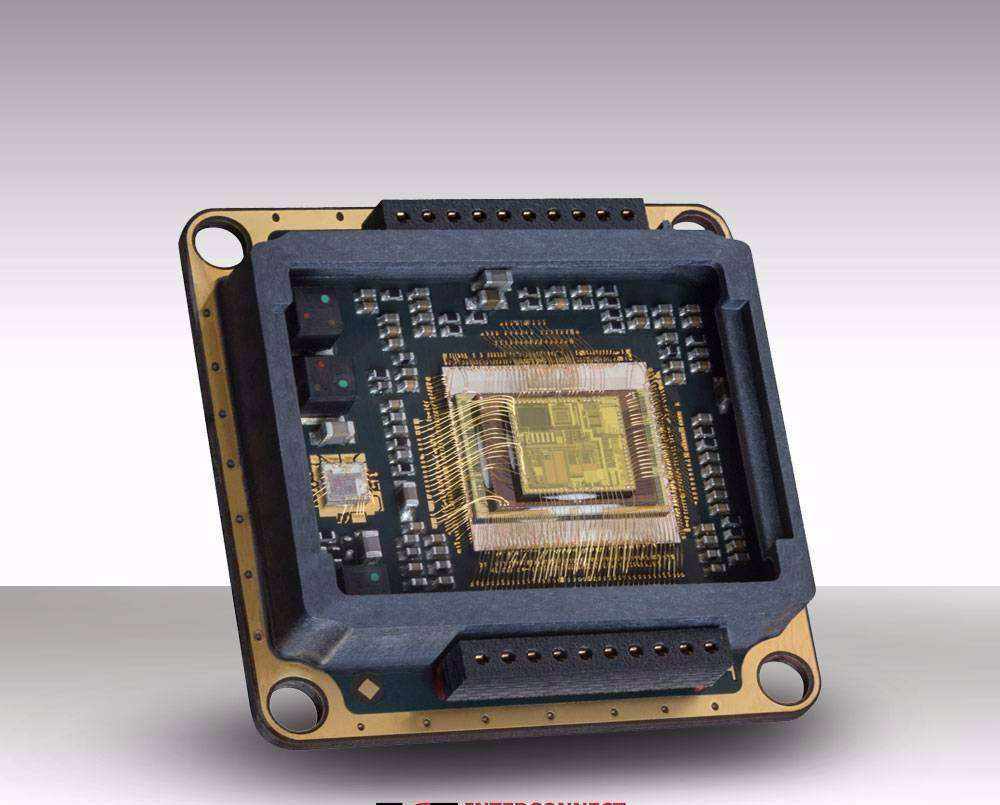

6 | 军工电子# h+ H9 f; @7 q | SiP技术顺应了军事电子的应用需求涉及了卫星、运载火箭、飞机、导弹、雷达、巨型计算机等军事装备,最具典型性的应用产品是各种频段的收发组件。 |

7 | 智能手机- O5 n, v! T+ m( B0 F, E | 手机中的RFPA是最常用SiP形式的。' l9 y- v( j6 \; u' T8 \ |

定义 | Soc特性 | SiP特性 |

效率 | 一个芯片就是一个系统, d% K) d& ^! D* t C. a, \8 O# I | 系统集成的各功能芯片及无源器件4 ]3 d* v) X) F, z9 m2 {% ~ |

工艺 | 受材料、IC不同工艺限制- O a9 H) H" }6 v2 S | 在基板上装配! X6 v* g1 Y R1 Z* w |

兼容性 | 更高的密度,更高速% M2 K0 x7 E; {" |# e V+ m | 可集成各种工艺的元件,如射频器件,RLC等1 q( m) |3 i) r" {# z |

难点 | Die尺寸较大- P& C) |1 W) x2 p | 测试较复杂; E6 z6 j. K( B1 T$ `" I" g |

成本 | 较高的开发成本 | 较低的开发成本 |

上市周期 | 开发周期长,良率较低3 |( L( l5 v! t+ m; Z | 开发周期短,良率较高 |

摩尔定律 | 摩尔定律发展方向' k8 P# f" C' W8 N2 F2 h9 }( Q | 超越了摩尔定律发展方向6 s% N4 B2 B9 `; S& A |

序号 | 优势 | 描述 |

1 | 封装效率高 | SiP封装技术在同一封装体内加多个芯片,大大减少了基板中芯片外围电路的面积,面相更小型化,高密度的基板设计。 |

2 | 产品上市周期短 | 由于SiP封装不同于Soc,无需版图级布局布线,从而减少了设计、验证和调试的复杂性,缩短了系统实现的时间。即使需要局部的改动设计也比Soc要简单容易得多。 |

3 | 兼容性佳 | SiP封装将不同的工艺、材料制作的芯片封成一个系统,可实现嵌入集成化无源元件,无线电和便携式电子产品中的无源元件至少可被嵌入30-50%,甚至可将Si、GaAs、InP等材料的的芯片组合后进行一体化封装。 |

4 | 系统成本低* |7 s6 |4 e' Z! X5 v# K% P | SiP可提供低功耗和低噪声的系统级设计,在较高的频率下工作可获得较宽的带宽。一个专用的集成电路系统,采用SiP封装技术可比Soc节省更多的系统设计和生产费用。& j' d. N6 T0 R% X# P |

5 | 物理尺寸小: d5 i; d2 ^7 G. S9 {$ d4 o2 u | SiP封装体的厚度不断减少,最先进的技术可实现五层堆叠芯片只有1.0mm厚的超薄封装。 |

6 | 电性能高 | SiP封装技术可以使多个封装器件在一个SiP系统中整合,可使总的焊点大为减少。也可以显着减小封装体积、重量。缩短元件的连接路线,从而使电性能得以提高。 |

7 | 低功耗$ u' f4 ~1 i6 }/ L; _ | SiP封装可提供低功耗、低噪音的系统级连接,在较高的频率下工作可获得几乎与Soc相等的汇流排宽度。( i% I5 h: J g |

8 | 稳定性好 | SiP封装具有良好的抗摔及抗腐蚀能力,具有高可靠性,借助EMI电磁屏蔽技术,可用于航空航天等复杂电磁场领域。' r- R7 X4 |1 K) b. r |

9 | 应用广泛0 P% x5 f( [8 v% r, w: s4 @" ? | 与传统芯片封装不同,SiP封装不仅可以处理数字系统,还可以应用于光通信、传感器以及微机电MEMS等领域。 |

| 欢迎光临 EDA365电子论坛网 (https://bbs.eda365.com/) | Powered by Discuz! X3.2 |