过去三年内,随着半导体行业并购的数量和金额创下新高(6),行业分析师和行业主编开始着重关注市场整合的趋势与影响。由于进场成本高,半导体行业发展速度放缓且竞争激烈,行业分析师认为半导体行业几乎不会再有新的市场参与者或业务模式。分析师们推测以下商业模式将会继续主导未来的半导体行业' M4 J; @% w+ d/ G" s

Ø IDM(国际整合元件制造商)- 拥有并保持半导体制造工厂。4 z) `' g" X3 u. X

Ø 无工厂器件供应商 - 专注于设计和IP,并依靠合同制造商来生产、组装并测试他们的产品。

Ø 晶圆代工厂 - 向IDM和无工厂供应商提供半导体生产服务& A. F. e8 l4 Z/ i/ n F0 D. e$ ^

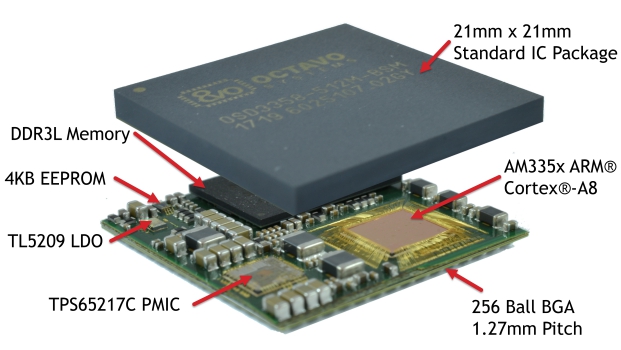

然而,SiP技术正在促使一种新的半导体商业模式出现。在这种商业模式中,由一家电子系统集成供应商,依靠先进的基板和微电子组装技术,通过集成各种半导体元器件去设计系统或子系统解决方案,然后用SiP封装形式去实现。Octavo Systems就是这种新型商业模型的一个例子(7)。图1展示了采用 21 x 21mm 256 BGA SiP的解决方案交付的Octavo OSD335x-SM产品(集成Bare Die和封装好的IC)。: L* A$ Y6 W# U9 t

Octavo Systems的网站是一个很好的信息来源,可以了解将SiP作为系统集成平台的发展趋势和解决方案,以此了解系统集成解决方案供应商这种新型商业模式的潜力,并探索可用于物联网(IoT)应用的产品创新与新服务。新的物联网应用正在各种行业涌现,包括银行业、制造业、零售业、医疗保健、运输业、公用事业和政府部门。预计到2020年,基于物联网的产品和服务收入将接近2700亿元(8)。1 U; c% ^; s7 O9 S' ]% P

9 t& _8 Z, }' [/ p! e- L

图1:Octavo系统OSD335x-SM 基于BGA SiP的产品4 ]. e k! k1 Y9 o5 D

; r; j! c! \3 G3 l* B, L, _

DDR3L Memory' L! U: j" j) k3 }; F

DDR3L 内存条$ ?: ^; j, j- J

21mm x 21mm Standard IC Package

21毫米 x 21毫米 标准IC封装

256 Ball BGA 1.27mm Pitch

256 球栅阵列 1.27毫米间距! `8 O8 n3 i- t

$ R8 M) r+ c {7 e$ j2 f

9. SiP 仅用于小型化

小型化是SiP的一个关键优势,但是性能和系统优化对于当今更高级别的集成来说同样重要。许多OEM系统供应商增加聘请了具有丰富微电子封装经验的工程师,以帮助他们有更好的定义系统结构和新的供应链,从而扩大对SiP 和模块解决方案的使用。这些OEM系统供应商能得到来自电气、热力和机械设计/仿真团队的支持,这些团队掌握了优化系统性能或可靠性所需的工具。半导体和OSAT供应商也扩大了他们的工程和设计/仿真团队,以应用更广泛的、先进的封装技术来开发新的SiP 解决方案。晶圆代工厂和电子制造服务(EMS)供应商也提高了技术和产能,提供如SiP 或模块的高度集成的解决方案。SiP 的使用正迅速扩展到如物联网连接的低性能产品应用,和诸如5G网站的高性能系统应用。, X j- w9 R0 V0 I& d; Q9 u

0 z/ q2 Z* w4 s; ^

10. SiP 受限于单一供应来源

这是不正确的。多源采购是大批量生产的常见要求。许多的委外封测代工厂(OSAT)具有先进的封装组装能力,并提供广泛的SiP封测服务。如果为了满足大批量生产或保证供应需要多源采购,建议制定供应链战略来应对:

Ø 复制完全相同或等同的要求。复制等同的要求可以使得供应商使用其验证过的材料,并为无源组件提供替代的供应商资源。

Ø 认证多个供应商资源。' u) L! K) r# b0 p

Ø 市场份额协议给到一定的生产量,和维持有能力的供应商资源。

Ø 公开分享设计或制造成本和质量改进。$ y) c" k+ V; w0 W( S% z

Ø 到期产品管理。

+ [% ] {! ?! P/ `* l9 Y

11. SiP仅在用于性能较低的产品应用时经济实惠7 [5 F m/ I, y5 U# W3 n

SiP解决方案适用于一系列广泛的产品应用。计算机、游戏机、通信和网络等产品应用需要高性能的解决方案,需要复杂的电气、导热和机械要求的同时保证产品寿命。SiP解决方案不仅限于低性能要求,随着3D SiP体系结构的出现,可以通过增加带宽、降低功耗、增加功能和集成混合半导体工艺节点来实现小型化和半导体集成,从而提高系统性能;产品体积更小,并加快了上市时间。