EDA365电子论坛网

标题: 集成电路封装专业术语整理 [打印本页]

作者: artic 时间: 2018-11-13 13:20

标题: 集成电路封装专业术语整理

' F c7 d; \' @6 P3 b- X集成电路封装专业术语整理

( h# H0 D2 Q* R3 O4 v8 I! U! p晶圆生产的目标

芯片的制造分为原料制作、单晶生长和晶圆的制造、集成电路晶圆的生产和集成电路的封装阶段。本节主要讲解集成电路封装阶段的部分。

- V* ` u, R8 G9 Z5 s9 d' i& w集成电路晶圆生产是在晶圆表面上和表面内制造出半导体器件的一系列生产过程。整个制造过程从硅单晶抛光片开始,到晶圆上包含了数以百计的集成电路戏芯片。

/ X; R$ \7 Z+ I; N% D0 K

下面,为了更好的理解芯片的结构,为大家介绍一些基本的晶圆术语。

8 b! R/ ]9 X3 q5 j1 k( ]% y+ f) n晶圆术语

: N3 ]7 ?+ e5 N; S$ N

0 o$ H S! ?- \9 M! t! }7 p6 B

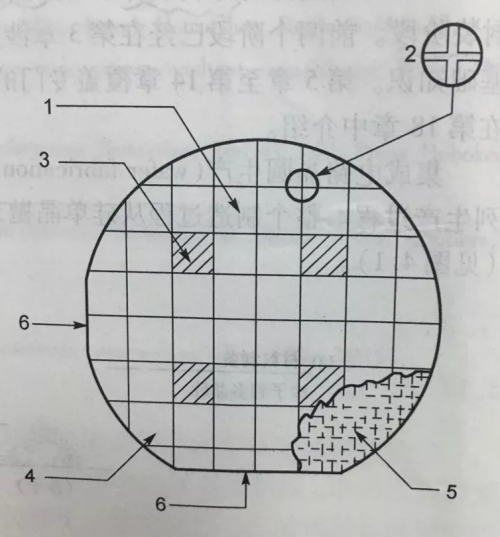

1. 芯片、器件、电路、微芯片或条码:所有这些名词指的是在晶圆表面占大部分面积的微芯片图形。

# v# x' _7 B; Q4 G* {2. 划片线或街区:这些区域是在晶圆上用来分隔不同芯片之间的间隔区。划片线通常是空白的,但有些公司在间隔区内放置对准标记,或测试的结构。

$ M* R2 U! P" M0 z: z# r3. 工程试验芯片和测试芯片:这些芯片与正式器件芯片或电路芯片不同。它包含特殊的器件和电路模块用于对晶圆生产工艺的电性测试。

. M0 t+ x4 R1 U+ |& f2 R' F

4. 边缘芯片:在晶圆的边缘上的一些掩模残缺不全的芯片而产生的面积损耗。由于单个芯片尺寸增大而造成的更多边缘浪费会由采用更大直径晶圆所弥补。推动半导体工业向更大直径晶圆发展的动力之一就是为了减少边缘芯片所占的面积。

3 w! y U% H4 F$ P( V4 O% K5. 晶圆的晶面:图中的剖面标示了器件下面的晶格构造。此图中显示的器件边缘与晶格构造的方向是确定的。

- h' h0 |! p% ~8 }6. 晶圆定位边/凹槽:例如图示的晶圆有主定位边和副定位边。300mm和450mm直径的晶圆都是用凹槽作为晶格导向的标识。这些定位边和凹槽在一些晶圆生产工艺中还辅助晶圆的套准。

4 f& @+ W; n0 F5 ^5 P$ L5 i d2 y芯片术语

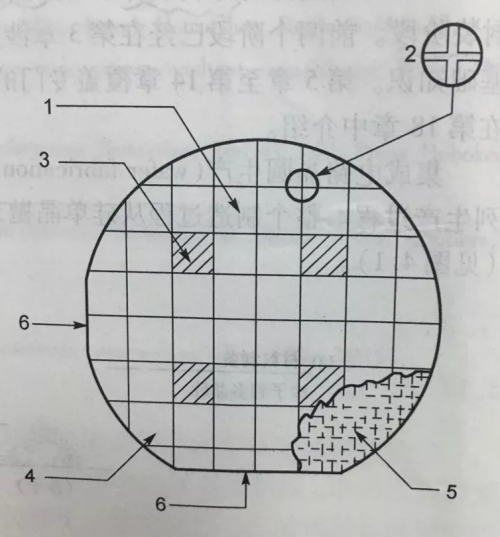

下图是一个中规模(MSI)/双极型集成电路的显微照片。之所以选择这个集成等级,是为了照片上能显示出电路的具体图形。对于更高集成度的电路,它的元件非常小,以至于在整个芯片的显微照片上无法辨认。

) M5 z2 E6 g* l2 R8 P

3 |2 d+ }8 w. \- g. B图中芯片的特性有:

9 V- b+ i( J2 F1 _1. 双极型晶体管

2. 电路的特定编号

3. 为连接芯片与管壳而备的压焊点

4. 压焊点上的一小块污染物

5. 金属表面导线

6. 划片线(芯片间的分割线)

7. 独立未连接的元件

8. 掩模版对准标记

9. 电阻

3 _& K0 J; c. f0 v6 t; d晶圆生产的基础工艺

在很多混合和集成电路设计。集成电路是基于一个少数晶体管结构和制造工艺。类似于车工业,这个工业生产的产品范围很广,从轿车到推土机。然而,金属成型、焊接、油漆等工艺对汽车厂都是通用的。在汽车厂内部,这些基本的工艺以不同的方式被应用,以制造出客户希望的产品。

- { ]6 V; q# [+ l" F

同样,芯片制造也是同样的。依此进行4个基本操作,以产生特定的芯片。这些操作是薄膜、图形化、掺杂和热处理。下图是一个硅栅晶体管的横截面。它说明了如何使用这些基本的操作并依此制造一个实际的半导体器件。

^* q" b; S2 k薄膜工艺

薄膜工艺是在晶圆表面形成薄膜的加工工艺。

4 v- d* _+ m! P9 @# e8 W2 M

各种技术用于二氧化硅层生长和各种材料的沉积。

9 r" y0 m+ s& D* v

Z; d' W/ O' e) Q" L通用的淀积技术是物理气相淀积、化学气相淀积、蒸发和溅射、分子束、外延生长、分子束外延和原子层淀积。使用电镀在高密度集成电路上淀积金属化层。

% K4 o( b+ R4 j. A- E0 C

图形化工艺

图形化工艺是通过一系列生产步骤将晶圆表面薄膜的特定部分除去工艺。从此之后,晶圆表面会留下带有微图形结构的薄膜。被除去部分的可能形状是薄膜内的空或是残留的岛状部分。

7 x/ Q" u/ c( G* N, J' t Y

图形化工艺也被未大家熟知的广掩模、掩模、光刻或微光刻。在晶圆制造过程中,晶体三极管、二极管、电容器和金属层的各种物理部件在晶圆表面或表层内构成。

3 V8 a2 p6 ?/ d3 f. F: \

7 v5 `3 ?/ h3 ?# r H

这些部件是每次在一个掩模版上生成的,并且结合生成薄膜及去除特定部分,通过图形化工艺过程,最终在晶圆上保留特征图形的部分。光刻生产的目标是根据电路设计的要求,生成尺寸精确的特征图形,且在晶圆表面的位置要正确,而且与其他层的关联也要正确。

; W2 s: E0 { E- i; l @ V# @图形化工艺是所有四个基本工艺中最关键的。图形化工艺确定了器件的关键尺寸。图形化工艺过程中的错误可能造成图形歪曲或套准不好,最终可转化为对器件的电特性产生影响。

' P& V9 j1 T# w8 A/ {

' t7 t& E' B' q X图形的错位也会导致类似的不良结果。图形化工艺中的另一个问题是缺陷。图形化工艺是高科技版本的照相术,只不过是在难以置信的微小尺寸小完成的。在制程中的污染物会造成缺陷。事实上由于图形化工艺在现代晶圆生产过程中要完成30层或更多,所以污染问题将会放大。

1 Q* [6 S% m# V. k

作者: yxlk 时间: 2018-11-13 13:38

嗯嗯 非常详细

作者: gaoxings 时间: 2018-11-13 14:00

收了

作者: wangmn 时间: 2018-11-16 10:33

谢谢分享

| 欢迎光临 EDA365电子论坛网 (https://bbs.eda365.com/) |

Powered by Discuz! X3.2 |