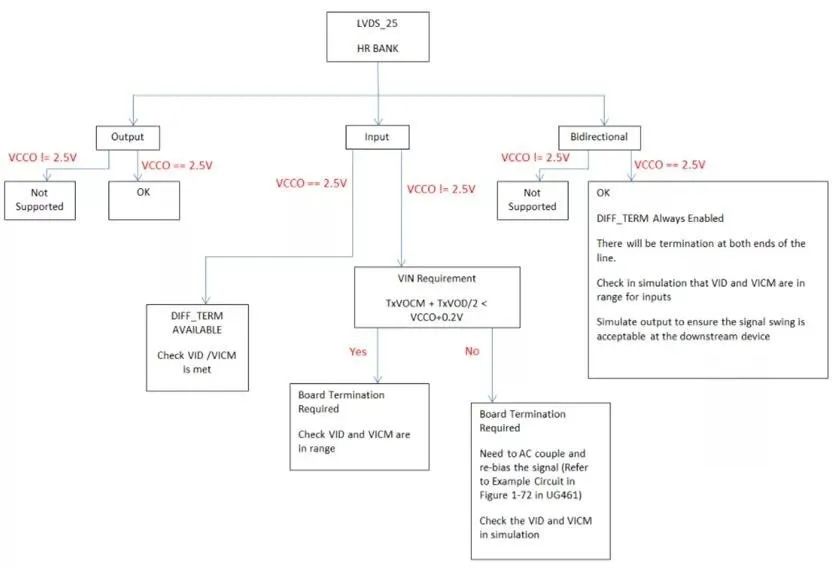

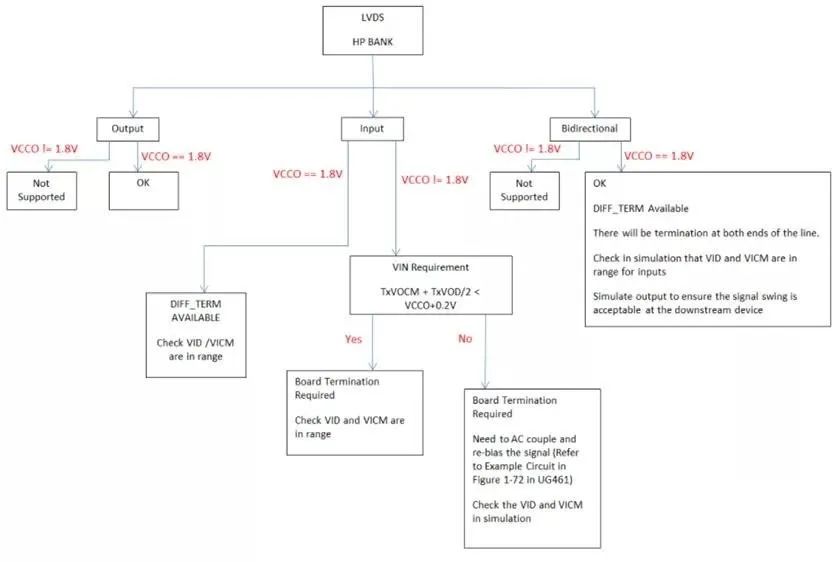

很多工程师在使用Xilinx开发板时都注意到了一个问题,就是开发板中将LVDS的时钟输入(1.8V电平)连接到了VCCO=2.5V或者3.3V的Bank上,于是产生了关于FPGA引脚与LVDS(以及LVDS-33,LVDS-25)信号相连时兼容性的问题,该专题就解决一下这类问题。总的来说,只要按照下面图 1和图 2流程进行判断即可。   『本文转载自网络,版权归原作者所有,如有侵权请联系删除』 |

/1

/1

关于我们|手机版|EDA365电子论坛网 ( 粤ICP备18020198号-1 )

GMT+8, 2025-8-4 19:54 , Processed in 0.125000 second(s), 27 queries , Gzip On.

地址:深圳市南山区科技生态园2栋A座805 电话:19926409050